やっと Vivado を使います。

今回は具体的な理解はさておき、とりあえずざっくり理解した上で構成を考えることをしてみました。なお、FPGA を最近いじり始めて間もないので理解がざっくりしています。ひょっとしたら記述が間違っているかも...その時は誰かコメントで教えて下さい!

参考資料

- PYNQ-Z1 Reference Manual - Digilent Reference

- 大まかなボードの構成はこちらに。

- PYNQ-Z1 ボードの回路図

- Arduino 端子から外部に配線を持っていく際に見ることになる。

- 使用した7セグLEDのデータシート

- ピン配置を見た。

- FPGAプログラミング大全 Xilinx編 第2版 - Amazon

- Xilinx の FPGA に初めて触れる人向けにおすすめの本らしい。購入して現在到着待ち。

そもそもの構成がわからん...

このボード、よく見ると色々できるようにたくさんの素子、コネクタが載っています。ただ、PS と PL の区別をつけるのは大切だと思いましたのでまとめます。

PS(Processing System)

そもそもこのボードに載っているチップにはマイコンがあります。ARM コアなんですが、ここから Python を経由して RAM やロジック部分にアクセスできるんですよね。

PYNQ とはそういう複数レイヤを跨いだプラットフォームを指すのであって、つまりレイヤが高すぎてなんにもわかりません。僕はとりあえず FPGA でロジック設計を味わいたいのよ。

PL(Programmable Logic)

これがいわゆる FPGA です。論理ゲート素子に対して LUT(Look-Up Table) を与えて回路を構成する感じのものです。これを求めていた...

最低限の環境に落とし込む

皆さん FPGA ボードでかなりすごいことをされている人が多いですよね。でも、この界隈、入門レヴェルと上級者の乖離が激しくないですか???

...ちょっと荒ぶりました。つまり、入門でLチカをしている人と、IkaLog などのすごい回路設計をされている人がいるけれど中間層が少ない気がする、ということです。

僕はその中間層である自覚はあります。多分。

前回の記事にも載せましたこの Qiita 記事ではなんか大層な ZYNQ7 Processing System やら Processor System Reset がブロック図で結線されていますけれど、そんなもの要らない訳です。

ここで必要なのはただ一つ。入力と出力の関係性です。

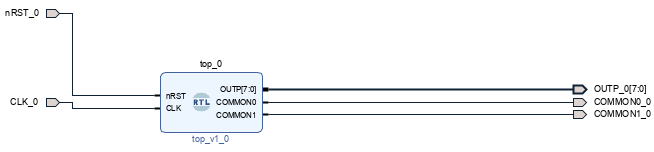

例えばこちらを御覧ください。僕が今現在 PYNQ-Z1 で動かしている回路のブロック図なんですけど(後日公開)、これで十分動いています。

そういえばこうやって TOP モジュールを単独で用意する作法っていいんですかね?まあ慣れないうちは GUI を使わないほうがいいっか。

やたら高級な IP (ペリフェラルのこと) はひとまずいらないわけですよ。こんな高級なものが最初からあったら訳が分からなくてやる気が失せてしまう。

これで皆さん安心しましたかね???僕が土日を犠牲にして研究した結果、この結論に至りました。ぜひこの結果に乗っかってください!

ロジック回路実装のためのフローを概説

深いことを考えずに書き込むまでに必要なフローを示します。

- Verilog 等で RTL 記述をする

- Block Design を開き、必要な結線をする。入出力ピンは Make External で外に出しておく

- Synthesis で各モジュールを論理合成

- Synthesized Design を開き、右上プルダウンから I/O Planning によってピン配置をする

- Implimentation を実行

- Bitstream と言われる、FPGA に書き込むのに必要なバイナリを生成

ざっくりとこんな感じです。RTL 記述を変更したとしても入出力ポートやその名前を変えていない場合は Block Design をやり直す必要はありません。

それぞれですが、僕は以下のような認識でいます。

- Synthesis(論理合成)は、記述したロジックおよびモジュール間の結線をいい感じに翻訳する作業

- Implimentation(実装)は、Synthesis したものを実際の入出力ピンと紐付ける作業(多分他にも色々している)

Bitstream生成時のエラー回避

一番多いエラーと思います。Synthesis や Impli が成功しているのに Bitstream 生成が失敗する場合です。

Vivado はすべての結線を I/O Planning で設定しないとエラーになるようで、使用しないピンでもこれが必要です(多分)。

そんなの知るかよ!と思うので、このエラーを握りつぶしてしまいましょう。

まずはどこかに tcl ファイルを生成します。僕は pre.tcl としました。そこに以下を書き込みます。ところで tcl って Tickle と読むらしいね。

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

これで OK です。あとはプロジェクト内で Flow Navigator 下部の Generate Bitstream を右クリックして Bitstream Settings... をクリックします。

tcl.pre でファイルを指定して Copy sources into project をチェックします。OK したら反映されます。作ったファイルはもういらないので削除してよし。

基本的なピン配置・クロック

回路図を見てください、と言ったらそれまでなので、ボード上にある基本的なポートの番号を便利のために載せておきます。

なお、様々な記事で紹介されている Processing System はあくまで PS (内部のマイコン)から動かす時に必要な IP なので、ひとまず無視しておきましょう。

プッシュスイッチ:Active Low です。

| ボート上の名前 | ポート名 |

|---|---|

| BTN0 | D19 |

| BTN1 | D20 |

| BTN2 | L20 |

| BTN3 | L19 |

スライドスイッチ:Active High です。

| ボート上の名前 | ポート名 |

|---|---|

| SW0 | M20 |

| SW1 | M19 |

BTNx 上の LED:緑色です。

| ボート上の名前 | ポート名 |

|---|---|

| LD0 | R14 |

| LD1 | P14 |

| LD2 | N16 |

| LD3 | M14 |

SWx 上の LED:三色 LED です。

| ボート上の名前 | ポート名 |

|---|---|

| LD4(R) | N15 |

| LD4(G) | G17 |

| LD4(B) | L15 |

| LD5(R) | M15 |

| LD5(G) | L14 |

| LD5(B) | G14 |

また、125MHz のクロックは H16 に供給されています。