結構時間を割きました。

FPGA を用いて、タイトルの通りカウンタ回路の作成に成功しましたのでこちらで報告します。

動作概要

簡単に言うと、1/100 秒までを高速にカウントする回路です。秒数は最高で 59.99 までカウントでき、次の瞬間にオーバーフローして 00.00 に戻ります。

部品としてはアクティブローのリセット信号としてプッシュスイッチ with Pull-up Resistor と、アノードコモンの2桁7セグLEDを用いました。その LEDは秋月で購入。

コードはこちらに上げてあります。

回路ブロック図・ピン配置

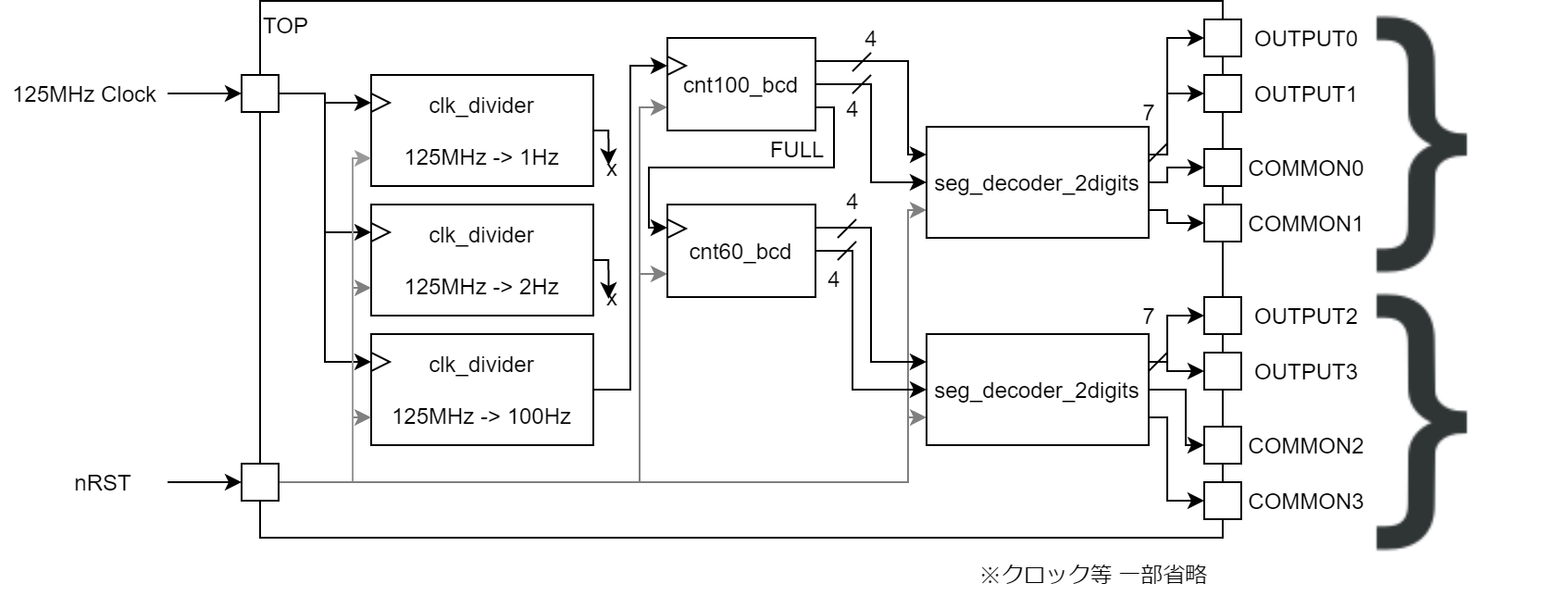

主なブロック図はこちらです。クロックを分周して回路に入力しました。入力先は100進カウンタと60進カウンタです。どちらも BCD 出力をしているので桁数の数字をそのまま転用可能になっています。

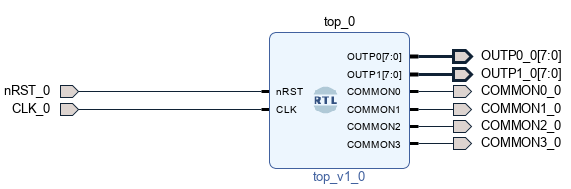

また、Vivado 上でのブロック図はこのように配線。まあ普通ですよ。

I/O Planning でのピン配置は以下。さすが 7セグLED ですね。ピン数が多すぎる。現状ブレッドボードに線を結構生やしているのでプリント基板でも起こしたいですねえ。

| 桁 | LED側ピン番号 | ボード側IO番号 | FPGA側ピン番号 |

|---|---|---|---|

| 01 | 1 | 0 | V15 |

| 01 | 2 | 1 | V13 |

| 01 | 3 | 2 | U17 |

| 01 | 4 | 3 | T14 |

| 01 | 5 | 4 | U12 |

| 01 | 7 | 5 | U13 |

| 01 | 8 | 6 | R16 |

| 01 | 10 | 7 | T15 |

| 01 | 6 | 34 | W10 |

| 01 | 9 | 35 | W6 |

| 23 | 1 | 8 | P18 |

| 23 | 2 | 9 | R17 |

| 23 | 3 | 10 | V5 |

| 23 | 4 | 11 | V17 |

| 23 | 5 | 12 | V18 |

| 23 | 7 | 13 | T16 |

| 23 | 8 | 26 | U5 |

| 23 | 10 | 27 | N17 |

| 23 | 6 | 36 | Y6 |

| 23 | 9 | 37 | Y7 |

また、nRST ピンはボード上の IO41(Y9) でした。

動作

こんな感じ。結構それっぽいでしょ。

あとはこれにスイッチ入力を加えればストップウォッチができますね!!