今度は IDE の機能である IP Core Generator で回路ブロックを生成する練習をしてみたいと思います。

このボードには PLL が載っているらしいですが(搭載チップである GW1N のデータシート参照)、これを使う IP の生成をしてみます。

IP Core Generatorの操作

ではやっていきましょう。まずはプロジェクトを作成します。

できましたか?そうしたらメニューバーから Tools -> IP Core Generator を選択すると、機能ブロックの一覧が並んだ画面が表示されると思います。

その一覧から画像のように PLL を選んでダブルクリックしましょう。

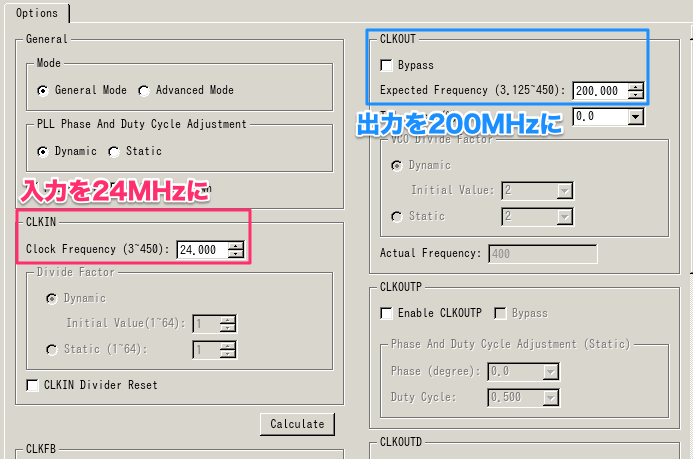

今回はオンボードの 24MHz クロックを なんとな〜く 200MHz にしてみたいと思うので、そういうふうに設定しましょうか。

そうしたら OK とか Yes を押しておきます。すると gowin_pll_tmp.v とか言うファイルが表示されますが、これは実際にインスタンス化する際にこう使ってくれよというテンプレートです。取り敢えず今すぐには使いません。

取り敢えず24MHzでLチカ

クロックが逓倍されたかを確認する前に、オンボードの 24MHz クロックでLチカをしておきましょう。以下のコードで、1秒間に1回 LED が反転します。

module delay_ms(input wire clk, input wire rstn, output reg tick);

reg[31:0] counter;

parameter max = 32'd24_000_000;

always @(posedge clk or negedge rstn) begin

if( ~rstn ) begin

counter <= 0;

tick <= 0;

end

else begin

counter <= counter + 1;

if( counter == max ) begin

tick <= 1;

counter <= 0;

end

else begin

tick <= 0;

end

end

end

endmodule

module main(input wire clk, input wire rstn, output reg led);

wire tick;

delay_ms delay(clk, rstn, tick);

always @(posedge tick or negedge rstn) begin

if( ~rstn ) begin

led <= 1;

end

else begin

led <= ~led;

end

end

endmodule

まあ普通のLチカですね。あくまでこれはただの動作確認。

PLLで逓倍された出力の200MHzでLチカ

続いて、main で PLL をインスタンス化し、そこから出てきたクロックを使うように設定してみましょう。

always 文直前までの部分を以下に置き換えてください。

wire clk_o;

Gowin_PLL pll(

.clkout(clk_o), //output clkout

.clkin(clk) //input clkin

);

wire tick;

delay_ms delay(clk_o, rstn, tick);

んで、これで動くかと思ったら動かなかったので、max = 32'd200_000_000 とすると、またさっきと同じような動きになります。

今回はさくっとでしたが、IP Core Generator の使い方を勉強したということで以上です。

次回あたりは LCD を使い始めていきたいなあ、、と思いますね。